# SPECIFICATION FOR LCD MODULE

Model No. <u>TM128160GKFWG</u>

| Prepared by:  | Date: |

|---------------|-------|

| Checked by:   | Date: |

| Verified by : | Date: |

| Approved by:  | Date: |

TIANMA MICROELECTRONICS CO., LTD

## **REVISION RECORD**

| Date | Ver. | Ref. Page | Revision No. | Revision Items |

|------|------|-----------|--------------|----------------|

|      |      |           |              |                |

|      |      |           |              |                |

|      |      |           |              |                |

|      |      |           |              |                |

|      |      |           |              |                |

|      |      |           |              |                |

|      |      |           |              |                |

|      |      |           |              |                |

|      |      |           |              |                |

|      |      |           |              |                |

|      |      |           |              |                |

|      |      |           |              |                |

|      |      |           |              |                |

|      |      |           |              |                |

|      |      |           |              |                |

|      |      |           |              |                |

# **1 General Specifications:**

| ITEM                  | CONTEN         | ΓS               | UNIT    |

|-----------------------|----------------|------------------|---------|

|                       | MAIN LCD       | SUB LCD          |         |

| LCD TYPE              | COLOR STN      | OLED             |         |

| LCD DUTY              | 1/160          | 1/40             |         |

| LCD BIAS              | 1/10           |                  |         |

| VIEWING DIRECTION     | 6:00           |                  | O'CLOCK |

| GLASS AREA(WXH)       | 36.25X49.80    | 26.8X21.2        | MM      |

| VIEWING AREA(WXH)     | 32.05X40.20    | 21.374X10.338    | MM      |

| ACTIVE AREA(WXH)      | 29.56X36.95    | 19.374X8.338     | MM      |

| NUMBER OF DOTS        | 128(R+G+B)X160 | 96X32(B)+96X7(Y) | MM      |

| DOTE SIZE(WXH)        | 0.221X0.221    | 0.182X0.182      | MM      |

| DOT PITCH(WXH)        | 0.231X0.231    | 0.202X0.202      | MM      |

| CONTROLLER            | HD66766        | SSD1301          |         |

| VBAT                  | 3.6~4.5V(TYP)  |                  |         |

| LCD OPERATING VOLTAGE | 16.8           | 9                | V       |

| OUTLINE DIMENSIONS    | REFER TO OUTI  | INE DRAWING ON   |         |

|                       | NEXT PAGE      |                  |         |

| BACKLIGHT             | LED(WHITE)     |                  |         |

| OPERATING TEMPERAT    | -20+70         | -20+60           |         |

| STORAGE TEMPERATURE   | -30+80         | -40+85           |         |

| WEIGHT                | TBD            |                  |         |

| DATA TRANSFER         | 8 BIT PARALLEL | I <sup>2</sup> C |         |

| POLARIZER MODE        | TRANSMISSIVE   |                  |         |

|                       | /NEGATIVE      |                  |         |

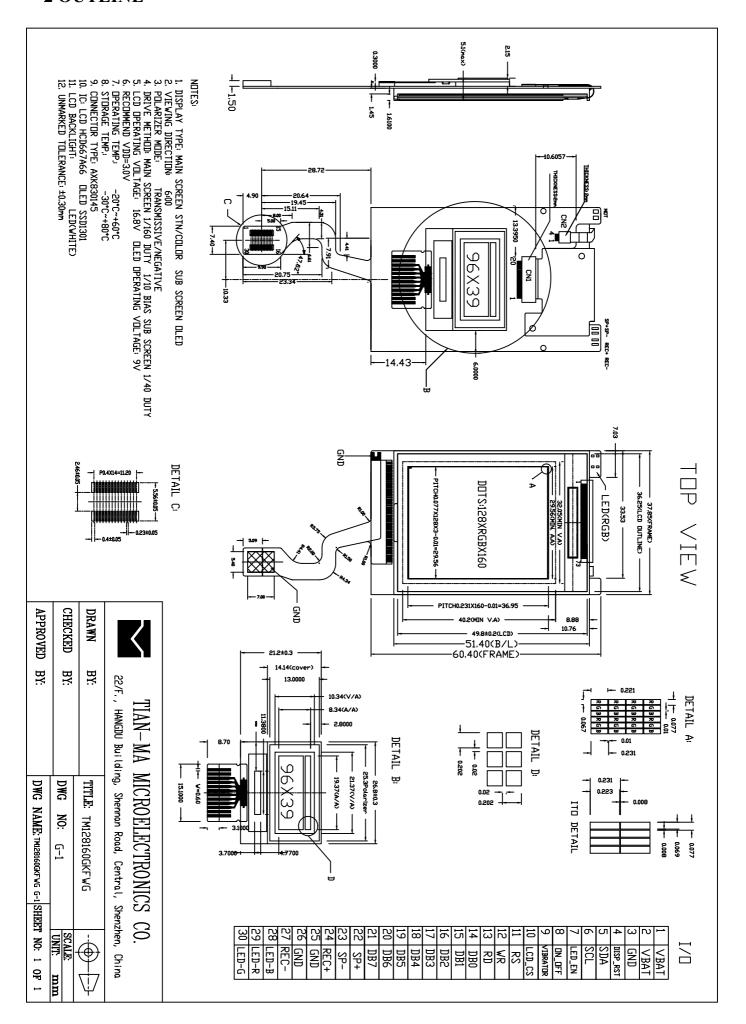

#### **2 OUTLINE**

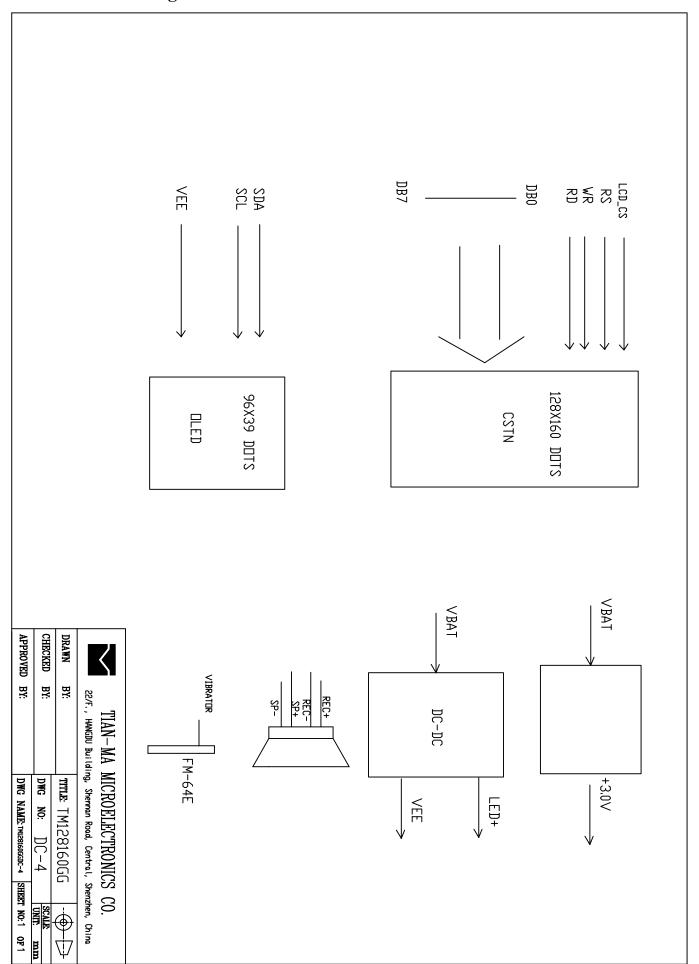

# 3. Circuit Block Diagram

# 4 Absolute Maximum Ratings(Ta=25 )

## MAIN\_LCD

| Item                           | Symbol    | Min. | Max.  | Unit | Remark       |

|--------------------------------|-----------|------|-------|------|--------------|

| Power Supply Voltage           | VDD - VSS | -0.3 | +4.6  | V    |              |

| LCD Driving Voltage            | VLCD      | -0.3 | +20.0 | v    |              |

| Operating Temperature<br>Range | ТОР       | -20  | +70   |      | No           |

| Storage Temperature<br>Range   | TST       | -30  | +80   |      | Condensation |

## OLED

| ITEM                 | MIN       | MAX        | UNIT | COMMENT |

|----------------------|-----------|------------|------|---------|

| Supply Voltage (VDD) | -0.3      | 4          | V    | Ta=25   |

| Supply Voltage (VEE) | 0         | VDD – 16.5 | V    | Ta=25   |

| Input Voltage (Vin)  | Vss - 0.3 | Vdd + 0.3  | V    | Ta=25   |

| Operating Temp.      | -20       | 60         |      |         |

| Storage Temp         | -40       | 85         |      |         |

# **5.** Electrical Specifications and Instruction Code (Vss=0v, Ta=25)

# 5.1 Electrical characteristics

| Parameter                                     | Symbol           | Condition | Min    | Тур  | Max    | Unit     |  |

|-----------------------------------------------|------------------|-----------|--------|------|--------|----------|--|

| Supply voltage for logic                      | VBAT             |           | 3.2    | 3.8  | 12     | V        |  |

| Supply voltage<br>for main LCD<br>(LCD DRIVE) | VLCD1            |           |        | 16.8 |        | V        |  |

| Supply voltage<br>for OLED<br>(OLED DRIVE)    | VLCD2            |           |        | 9    |        | V        |  |

| Input voltage'H'                              | MAIN             | VDD=3.0V  | 0.8VDD |      | VDD    | V        |  |

| Level(V <sub>IH</sub> )                       | SUB              | VDD=3.0V  | 0.8VDD |      | VDD    | <b>v</b> |  |

| Input voltage'L'                              | MAIN             | VDD=3.0V  | 0      |      | 0.2VDD | V        |  |

| Level(V <sub>IL</sub> )                       | SUB              | VDD=3.0V  | 0      |      | 0.2VDD | <b>'</b> |  |

| Supply current                                | MAIN             | VDD=3.0V  |        |      | 2.5    | mA       |  |

| (Logic) I <sub>DD</sub>                       | SUB              | VDD=3.0V  |        | 0.5  | 1      |          |  |

| Supply Voltage (LED)                          | $V_{LED}$        |           |        | 9.9  |        | V        |  |

| Supply current (LED)                          | I <sub>LED</sub> |           |        | 15.0 | 20.0   | mA       |  |

# 5.2 Interface Signals

| PinNo. | Symbo 1  | Level | Description                       |

|--------|----------|-------|-----------------------------------|

| 1      | VBAT     | Н     | Power supply                      |

| 2      | VBAT     | Н     | Power supply                      |

| 3      | GND      | L     | GROUND                            |

| 4      | DISP—RST | H/L   | Reset pin L: active               |

| 5      | SDA      | H/L   | I <sup>2</sup> c-BUS Data signal  |

| 6      | SCL      | H/L   | I <sup>2</sup> c-BUS Clock signal |

| 7      | LED-EN   | H/L   | Led enable pin L:active           |

| 8      | ON-OFF   | H/L   | VDD on or off. H: active          |

| 9      | VIBRATOR | H/L   | VIBRATOR control pin.             |

| 10     | LCD-CS   | H/L   | LCD Chip select pin               |

| 11     | RS       | H/L   | Index select/Data command select  |

| 12     | WR       | H/L   | Write operation(8080 system)      |

| 13     | RD       | H/L   | Read operation(8080 system)       |

| 14     | DB0      | H/L   | Data bus bit 0                    |

| 15     | DB1      | H/L   | Data bus bit 1                    |

| 16     | DB2      | H/L   | Data bus bit 2                    |

| 17     | DB3      | H/L   | Data bus bit 3                    |

| 18     | DB4      | H/L   | Data bus bit 4                    |

| 19     | DB5      | H/L   | Data bus bit 5                    |

| 20     | DB6      | H/L   | Data bus bit 6                    |

| 21     | DB7      | H/L   | Data bus bit 7                    |

| 22     | SP+      | H/L   | Speak input pin(+)                |

| 23     | SP-      | H/L   | Speak input pin(-)                |

| 24     | REC+     | H/L   | Receive input pin(+)              |

| 25     | GND      | L     | GROUND                            |

| 26     | GND      | L     | GROUND                            |

| 27     | REC-     | H/L   | Receive input pin(-)              |

| 28     | LED-B    | H/L   | Blue led control pin              |

| 29     | LED-G    | H/L   | Green led control pin             |

| 30     | LED-R    | H/L   | Red led control pin               |

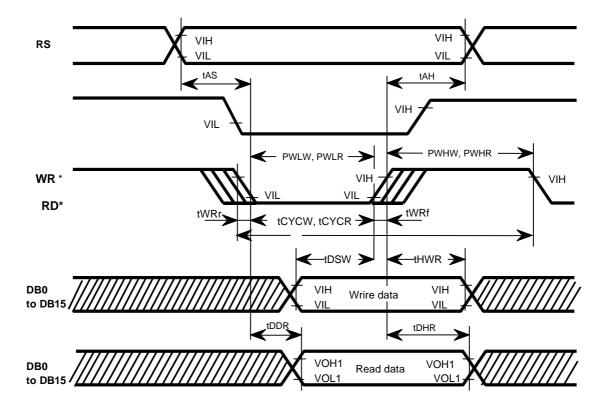

# 5.3 Interface Timing Chart

## HITACH HD66766 INTERFACE PROTOCOL

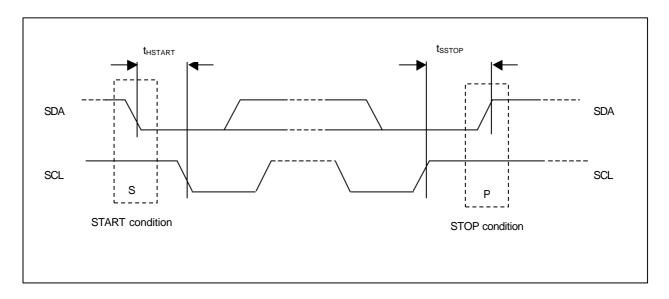

#### SOLOMON SSD1301 INTERFACE

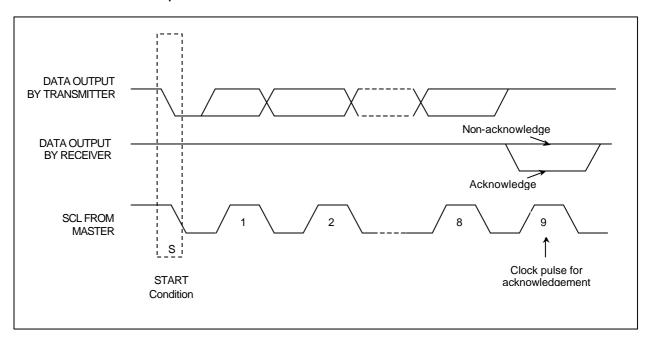

#### MPU I<sup>2</sup>C Interface

The  $lap{l}^2C$  communication interface consists of slave address bit SA0 ( $D_5$ ),  $lap{l}^2C$ -bus data signal SDA ( $D_0$  for output and  $D_1$  for input) and  $lap{l}^2C$ -bus clock signal SCL ( $D_4$ ). Both the data and clock signals must be connected to pull-up resistors. There are also five input signals including, RES#, CS1#, P/S#, CS2, SP#, which is used for the initialization of device.

#### a) Slave address bit (SA0)

SSD1301 has to recognize the slave address before transmitting or receiving any information by the l<sup>2</sup>C-bus. The device will respond to the slave address following by the slave address bit ("SA0" bit) and the read/write select bit ("R/W#" bit) with the following byte format,

$b_7 \ b_6 \ b_5 \ b_4 \ b_3 \ b_2 \ b_1 \ b_0$

0 1 1 1 1 0 SA0 R/W#

- "SA0" bit provides an extension bit for the slave address. Either "0111100" or "0111101", can be selected as the slave address of SSD1301.

- "R/W#" bit is used to determine the operation mode of the l<sup>2</sup>C-bus interface. R/W#=1, it is in read mode. R/W#=0, it is in write mode.

- b) I<sup>2</sup>C-bus data signal (SDA)

- SDA acts as a communication channel between the transmitter and the receiver. The data and the acknowledgement are sent through the SDA. If SDA in is connected to the "SDA out", the device becomes fully PC bus compatible. It should be noticed that the ITO track resistance and the pulled-up resistance at "SDA" pin becomes a voltage potential divider. As a result, the acknowledgement would not be possible to attain a valid logic 0 level in "SDA". The "SDA out" pin may be disconnected from the "SDA in" pin. With such arrangement, the acknowledgement signal will be ignored in the PC-bus.

- c) I<sup>2</sup>C-bus clock signal (SCL)

- The transmission of information in the  $l^2$ C-bus is following a clock signal, SCL. Each transmission of data bit is taken place during a single clock period of SCL.

#### I<sup>2</sup>C-bus Write data and read register status

The  $^{\circ}$ C-bus interface gives access to write data and command into the device. Please refer to Figure 8 for the write mode of  $^{\circ}$ C-bus in chronological order.

I<sup>2</sup>C-bus data format

#### **SOLOMON SSD1301 INTERFACE**

#### Write mode for I2C

- The master device initiates the data communication by a start condition. The definition of the start condition is shown in Figure 9. The start condition is established by pulling the SDA from high to low while the SCL stays high.

- 2) The slave address is following the start condition for recognition use. For the SSD1301, the slave address is either "b0111100" or "b0111101" by changing the SA0 to high or low.

- 3) The write mode is established by setting the R/W# bit to logic "0"

- 4) An acknowledgement signal will be generated after receiving one byte of data, including the slave address and the R/W# bit. Please refer to the Figure 10 for the graphical representation of the acknowledge signal. The acknowledge bit is defined as the SDA line is pulled down during the high period of the acknowledgement related clock pulse.

- 5) After the transmission of the slave address, either the control byte or the data byte may be sent across the SDA. A control byte mainly consists of Co and D/C# bits following by six "0" 's.

- a. If the Co bit is set as logic "0", the transmission of the following information will contain data bytes only.

- b. The D/C# bit determines the next data byte is acted as a command or a data. If the D/C# bit is set to logic "0", it defines the following data byte as a command. If the D/C# bit is set to logic "1", it defines the following data byte as a data which will be stored at the GDDRAM. The GDDRAM column address pointer will be increased by one automatically after each data write.

- 6) Acknowledge bit will be generated after receiving each control byte or data byte.

- 7) The write mode will be finished when a stop condition is applied. The stop condition is also defined in Figure 9. The stop condition is established by pulling the "SDA in" from low to high while the "SCL" stays high.

#### Definition of the start and stop condition

Definition of the acknowledgement condition

## 5.4 Instruction code

## Instruction List(HD66766)

|             |                                               |         |    | Upp      | er Co    | de       |          |          |          |          |          | Low      | er Co    | de       |          |          |          |          |          |                                                                                                                                                                                                                                            |          |       |

|-------------|-----------------------------------------------|---------|----|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|

| Reg.<br>No. | Register<br>Name                              | R/<br>W | RS | DB<br>15 | DB<br>14 | DB<br>13 | DB<br>12 | DB<br>11 | DB<br>10 | DB<br>9  | DB<br>8  | DB<br>7  | DB<br>6  | DB<br>5  | DB<br>4  | DB<br>3  | DB<br>2  | DB<br>1  | DB<br>0  | Description                                                                                                                                                                                                                                |          |       |

| IR          | Index                                         | 0       | 0  | *        | *        | *        | *        | *        | *        | *        | *        | *        | ID6      | ID5      | ID4      | ID3      | ID2      | ID1      | ID0      | Sets the index register value.                                                                                                                                                                                                             | 0        | Note1 |

| SR          | Status read                                   | 1       | 0  | L7       | L6       | L5       | L4       | L3       | L2       | L1       | L0       | 0        | C6       | C5       | C4       | C3       | C2       | Cl       | C0       | Reads the driving raster-row position (L7–0) and contrast setting (C6–0).                                                                                                                                                                  | 0        | =     |

| R00h        | Start<br>oscillation                          | 0       | 1  | *        | *        | *        | *        | *        | *        | *        | *        | *        | *        | *        | *        | *        | *        | *        | 1        | Starts the oscillation mode.                                                                                                                                                                                                               | 10<br>ms | Note1 |

|             | Device<br>code read                           | 1       | 1  | 0        | 0        | 0        | 0        | 0        | 1        | 1        | 1        | 0        | 1        | 1        | 0        | 0        | 1        | 1        | 0        | Reads 0766H.                                                                                                                                                                                                                               | 0        | ="    |

| R01h        | Driver<br>output<br>control                   | 0       | 1  | 0        | 0        | 0        | 0        | 0        | 0        | CM<br>S  | SGS      | 0        | 0        | 0        | NL4      | NL3      | NL2      | NL1      | NL0      | Sets the common driver shift<br>direction (CMS), segment driver<br>shift direction (SGS) and driving<br>duty ratio (NL4-0).                                                                                                                | 0        | -     |

| R02h        | LCD-<br>driving-<br>waveform<br>control       | 0       | 1  | 0        | 0        | 0        | 0        | 0        | RST      | B/C      | EOR      | 0        | 0        | NW<br>5  | NW<br>4  | NW<br>3  | NW<br>2  | NW<br>1  | NW<br>0  | Sets LCD drive AC waveform (B/C), and EOR output (EOR) or the number of n-raster-rows (NW5-0) at C-pattern AC drive.                                                                                                                       | 0        | =     |

| R03h        | Power<br>control 1                            | 0       | 1  | BS3      | BS2      | BS1      | BS0      | BT3      | BT2      | BTI      | вто      | 0        | DC2      | DC1      | DC0      | API      | AP0      | SLP      | STB      | Sets the sleep mode (SLP), standby<br>mode (STB), LCD power on (API–<br>0), boosting cycle (DC2–0),<br>boosting output multiplying factor<br>(BT2–0), operation of voltage<br>inverting circuit (BT3) and LCD<br>drive bias value (BS3–0). | 0        | -     |

| R04h        | Contrast<br>control                           | 0       | 1  | 0        | 0        | 0        | 0        | 0        | VR2      | VR1      | VR0      | 0        | CT6      | CT5      | CT4      | CT3      | CT2      | CT1      | CT0      | Sets the regulator adjustment (VR2–0) and contrast adjustment (CT6–0).                                                                                                                                                                     | 0        | ="    |

| R05h        | Entry mode                                    | 0       | 1  | SPR      | 0        | 0        | 0        | 0        | 0        | HWM      | 0        | 0        | 0        | I/D1     | I/D0     | AM       | LG2      | LG1      | LG0      | Specifies AC counter mode (AM), increment/decrement mode (I/D1 – 0), high-speed write mode (HWM).                                                                                                                                          | 0        | Note2 |

| R06h        | Compare<br>Resister                           | 0       | 1  | CP1<br>5 | CP1<br>4 | CP1<br>3 | CP1 2    | CP1      | CP1<br>0 | CP9      | CP8      | CP7      | CP6      | CP5      | CP4      | CP3      | CP2      | CP1      | CP0      | Specifies the compare resister (CP15-0),                                                                                                                                                                                                   | 0        | -     |

| R07h        | Display<br>control                            | 0       | 1  | 0        | 0        | 0        | 0        | 0        | VLE2     | VLE1     | SPT      | 0        | 0        | 0        | 0        | B/W      | REV      | DI       | D0       | Specifies display on (D1-0), black-<br>and-white reversed display (REV),<br>pixel on/off mode (ALB), screen<br>division driving (SPT) and vertical<br>scroll .(VLE2-1)                                                                     | 0        | -     |

| R0Bh        | Frame<br>frequency<br>control                 | 0       | 1  | 0        | 0        | 0        | 0        | 0        | 0        | DIV<br>1 | DIV<br>0 | 0        | 0        | 0        | 0        | RTN<br>3 | RTN<br>2 | RTN<br>1 | RTN<br>0 | Specifies the line retrace period (RTN3-0) and operating clock frequency division ratio (DIV1-0).                                                                                                                                          | 0        | -     |

| R0Ch        | Power<br>control 2                            | 0       | 1  | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | VC2      | VC1      | VC0      | Sets the adjustment factor for the Vci voltage (VC2-0).                                                                                                                                                                                    | 0        | ="    |

| R11h        | Vertical<br>scroll<br>control                 | 0       | 1  | VL2<br>7 | VL2<br>6 | VL2<br>5 | VL2<br>4 | VL2<br>3 | VL2<br>2 | VL2<br>1 | VL2<br>0 | VL1<br>7 | VL1<br>6 | VL1<br>5 | VL1<br>4 | VL1<br>3 | VL1<br>2 | VL1      | VL1<br>0 | Sets the 1 <sup>st</sup> screen display start<br>raster-row (VL17-10) and 2 <sup>nd</sup><br>screen display start raster-row<br>(VL27-20).                                                                                                 | 0        | =     |

| R14h        | 1 <sup>st</sup> screen<br>driving<br>position | 0       | 1  | SE<br>17 | SE<br>16 | SE<br>15 | SE<br>14 | SE<br>13 | SE<br>12 | SE<br>11 | SE<br>10 | SS<br>17 | SS<br>16 | SS<br>15 | SS<br>14 | SS<br>13 | SS<br>12 | SS<br>11 | SS<br>10 | Sets the 1 <sup>st</sup> screen driving start position (SS17–10) and 1 <sup>st</sup> screen driving end position (SE17–10).                                                                                                                | 0        | -     |

| R15h        | 2 <sup>nd</sup> screen<br>driving<br>position | 0       | 1  | SE<br>27 | SE<br>26 | SE<br>25 | SE<br>24 | SE<br>23 | SE<br>22 | SE<br>21 | SE<br>20 | SS<br>27 | SS<br>26 | SS<br>25 | SS<br>24 | SS<br>23 | SS<br>22 | SS<br>21 | SS<br>20 | Sets 2 <sup>nd</sup> screen driving start position (SS27–20) and 2 <sup>nd</sup> screen driving end position (SE27–20).                                                                                                                    | 0        | -     |

| R16h        | Horizontal<br>RAM<br>address<br>position      | 0       | 1  | HE<br>A7 | HEA<br>6 | HEA<br>5 | HEA<br>4 | HEA<br>3 | HEA<br>2 | HEA<br>1 | HEA<br>0 | HSA<br>7 | HSA<br>6 | HSA<br>5 | HSA<br>4 | HSA<br>3 | HSA<br>2 | HSA<br>1 | HSA<br>0 | Sets start (HSA7-0) and end<br>(HEA7-0) of the horizontal RAM<br>address range.                                                                                                                                                            | 0        | -     |

| R17h        | Vertical<br>RAM<br>address<br>position        | 0       | 1  | VEA      | VEA<br>6 | VEA<br>5 | VEA<br>4 | VEA<br>3 | VEA<br>2 | VEA<br>1 | VEA<br>0 | VSA<br>7 | VSA<br>6 | VSA<br>5 | VSA<br>4 | VSA<br>3 | VSA<br>2 | VSA<br>1 | VSA<br>0 | Sets start (VSA7-0) and end (VEA7-0) of the vertical RAM address range.                                                                                                                                                                    | 0        | -     |

| R20h        | RAM write<br>data mask                        | 0       | 1  | WM<br>15 | WM<br>14 | WM<br>13 | WM<br>12 | WM<br>11 | WM<br>10 | WM<br>9  | WM<br>8  | WM<br>7  | WM<br>6  | WM<br>5  | WM<br>4  | WM<br>3  | WM<br>2  | WM<br>1  | WM<br>0  | Specifies write data mask (WM15–0) at RAM write.                                                                                                                                                                                           | 0        | =     |

|             |                                               |         |    |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |                                                                                                                                                                                                                                            |          | -     |

# Instruction List (cont.)

| Upper Code | Lower Code |

|------------|------------|

| • •        |            |

| Reg. | Register                             |         |    | DB | DB | DB        | DB        | DB        | DB        | DB        | DB        | DB | DB | DB        | DB        | DB        | DB        | DB        | DB        | -                                                          | Execu-<br>tion |

|------|--------------------------------------|---------|----|----|----|-----------|-----------|-----------|-----------|-----------|-----------|----|----|-----------|-----------|-----------|-----------|-----------|-----------|------------------------------------------------------------|----------------|

| No.  | Name                                 | R/<br>W | RS | 15 | 14 | 13        | 12        | 11        | 10        | 9         | 8         | 7  | 6  | 5         | 4         | 3         | 2         | 1         | 0         | Description                                                | Cycle          |

| R21h | RAM<br>address set                   | 0       | 1  |    |    |           | AD15-     | 8 (upper  | )         |           |           |    |    | ADo       | 5–0 (lov  | /er)      |           |           |           | Initially set the RAM address to the address counter (AC). | 0              |

| R22  | RAM data<br>write                    | 0       | 1  |    |    | V         | Vrite da  | ta (uppe  | r)        |           |           |    |    | 1         | Vrite da  | ta (lowe  | er)       |           |           | Writes data to the RAM.                                    | 0              |

|      | RAM data<br>read                     | 1       | 1  |    |    | F         | Read dat  | a (uppe   | r)        |           |           |    |    | 1         | Read da   | ta (lowe  | r)        |           |           | Reads data from the RAM.                                   | 0              |

| R30h | Grayscale<br>palette<br>control (1)  | 0       | 1  | 0  | 0  | PK15      | PK14      | PK13      | PK12      | PK11      | PK10      | 0  | 0  | PK05      | PK04      | PK03      | PK02      | PK01      | PK00      | Specifies the grayscale palette.                           | 0              |

| R31h | Grayscale<br>palette<br>control (2)  | 0       | 1  | 0  | 0  | PK35      | PK34      | PK33      | PK32      | PK31      | PK30      | 0  | 0  | PK25      | PK24      | PK23      | PK22      | PK21      | PK20      | Specifies the grayscale palette.                           | 0              |

| R32h | Grayscale<br>palette<br>control (3)  | 0       | 1  | 0  | 0  | PK55      | PK54      | PK53      | PK52      | PK51      | PK50      | 0  | 0  | PK45      | PK44      | PK43      | PK42      | PK41      | PK40      | Specifies the grayscale palette.                           | 0              |

| R33h | Grayscale<br>palette<br>control (4)  | 0       | 1  | 0  | 0  | PK75      | PK74      | PK73      | PK72      | PK71      | PK70      | 0  | 0  | PK65      | PK64      | PK63      | PK62      | PK61      | PK60      | Specifies the grayscale palette.                           | 0              |

| R34h | Grayscale<br>palette<br>control (5)  | 0       | 1  | 0  | 0  | PK95      | PK94      | PK93      | PK92      | PK91      | PK90      | 0  | 0  | PK85      | PK84      | PK83      | PK82      | PK81      | PK80      | Specifies the grayscale palette.                           | 0              |

| R35h | Grayscale<br>palette<br>control (6)  | 0       | 1  | 0  | 0  | PK<br>115 | PK<br>114 | PK<br>113 | PK<br>112 | PK<br>111 | PK<br>110 | 0  | 0  | PK<br>105 | PK<br>104 | PK<br>103 | PK<br>102 | PK<br>101 | PK<br>100 | Specifies the grayscale palette.                           | 0              |

| R36h | Grayscale<br>palette<br>control (7)  | 0       | 1  | 0  | 0  | PK<br>135 | PK<br>134 | PK<br>133 | PK<br>132 | PK<br>131 | PK<br>130 | 0  | 0  | PK<br>125 | PK<br>124 | PK<br>123 | PK<br>122 | PK<br>121 | PK<br>120 | Specifies the grayscale palette.                           | 0              |

| R37h | Grayscale<br>palette<br>control (8)  | 0       | 1  | 0  | 0  | PK<br>155 | PK<br>154 | PK<br>153 | PK<br>152 | PK<br>151 | PK<br>150 | 0  | 0  | PK<br>145 | PK<br>144 | PK<br>143 | PK<br>142 | PK<br>141 | PK<br>140 | Specifies the grayscale palette.                           | 0              |

| R38h | Grayscale<br>palette<br>control (9)  | 0       | 1  | 0  | 0  | PK<br>175 | PK<br>174 | PK<br>173 | PK<br>172 | PK<br>171 | PK<br>170 | 0  | 0  | PK<br>165 | PK<br>164 | PK<br>163 | PK<br>162 | PK<br>161 | PK<br>160 | Specifies the grayscale palette.                           | 0              |

| R39h | Grayscale<br>palette<br>control (10) | 0       | 1  | 0  | 0  | PK<br>195 | PK<br>194 | PK<br>193 | PK<br>192 | PK<br>191 | PK<br>190 | 0  | 0  | PK<br>185 | PK<br>184 | PK<br>183 | PK<br>182 | PK<br>181 | PK<br>180 | Specifies the grayscale palette.                           | 0              |

| R3Ah | Grayscale<br>palette<br>control (11) | 0       | 1  | 0  | 0  | PK<br>215 | PK<br>214 | PK<br>213 | PK<br>212 | PK<br>211 | PK<br>210 | 0  | 0  | PK<br>205 | PK<br>204 | PK<br>203 | PK<br>202 | PK<br>201 | PK<br>200 | Specifies the grayscale palette.                           | 0              |

| R3Bh | Grayscale<br>palette<br>control (12) | 0       | 1  | 0  | 0  | PK<br>235 | PK<br>234 | PK<br>233 | PK<br>232 | PK<br>231 | PK<br>230 | 0  | 0  | PK<br>225 | PK<br>224 | PK<br>223 | PK<br>222 | PK<br>221 | PK<br>220 | Specifies the grayscale palette.                           | 0              |

| R3Ch | Grayscale<br>palette<br>control (13) | 0       | 1  | 0  | 0  | PK<br>255 | PK<br>254 | PK<br>253 | PK<br>252 | PK<br>251 | PK<br>250 | 0  | 0  | PK 255    | PK<br>244 | PK<br>243 | PK<br>242 | PK<br>241 | PK<br>240 | Specifies the grayscale palette.                           | 0              |

| R3Dh | Grayscale<br>palette<br>control (14) | 0       | 1  | 0  | 0  | PK<br>275 | PK<br>274 | PK<br>273 | PK<br>272 | PK<br>271 | PK<br>270 | 0  | 0  | PK<br>265 | PK<br>264 | PK<br>263 | PK<br>262 | PK<br>261 | PK<br>260 | Specifies the grayscale palette.                           | 0              |

| R3Eh | Grayscale<br>palette<br>control (15) | 0       | 1  | 0  | 0  | PK<br>295 | PK<br>294 | PK<br>293 | PK<br>292 | PK<br>291 | PK<br>290 | 0  | 0  | PK<br>285 | PK<br>284 | PK<br>283 | PK<br>282 | PK<br>281 | PK<br>280 | Specifies the grayscale palette.                           | 0              |

| R3Fh | Grayscale<br>palette<br>control (16) | 0       | 1  | 0  | 0  | PK<br>315 | PK<br>314 | PK<br>313 | PK<br>312 | PK<br>311 | PK<br>310 | 0  | 0  | PK<br>305 | PK<br>304 | PK<br>303 | PK<br>302 | PK<br>301 | PK<br>300 | Specifies the grayscale palette.                           | 0              |

Note:

<sup>1. &</sup>quot;\*" means doesn't matter.

<sup>2.</sup> High-speed write mode is available only for the RAM writing.

## **COMMAND TABLE (SSD1301)**

Command table (D/C# =0, R/W#(WR#)=0, E (RD#)=1)

| Bit Pattern                                                                                                                         | Command                           | Description                                                                                                                                                                                        |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 0000X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                                                                     | Set Lower Column Address          | Set the lower nibble of the column address register using $X_3X_2X_1X_0$ as data bits. The initial display line register is reset to 0000b after POR.                                              |  |  |  |  |  |  |  |

| 0001X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                                                                     | Set Higher Column Address         | Set the higher nibble of the column address register using $X_3X_2X_1X_0$ as data bits. The initial display line register is reset to 0000b after POR.                                             |  |  |  |  |  |  |  |

| 01X <sub>5</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                                         | Set Display Start Line            | Set display RAM display start line register from 063 using $X_5X_4X_3X_2X_1X_0$ . Display start line register is reset to 000000 during POR.                                                       |  |  |  |  |  |  |  |

| 10000001<br>X <sub>7</sub> X <sub>6</sub> X <sub>5</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | Set Contrast Control Register     | Double byte command to select 1 out of 256 contrast steps. Contrast increases as $X_6X_5X_4X_3X_2X_1X_0$ is increased from 00000000b to 11111111b. $X_7X_6X_5X_4X_3X_2X_1X_0$ =10000000b after POR |  |  |  |  |  |  |  |

| 1010000X <sub>0</sub>                                                                                                               | Set Segment Re-map                | X <sub>0</sub> =0: column address 00H is mapped to SEG0 (POR)<br>X <sub>0</sub> =1: column address 83H is mapped to SEG0                                                                           |  |  |  |  |  |  |  |

| 1010010X <sub>0</sub>                                                                                                               | Set Entire Display On/Off         | X <sub>0</sub> =0: normal display (POR)<br>X <sub>0</sub> =1: entire display on                                                                                                                    |  |  |  |  |  |  |  |

| 1010011X <sub>0</sub>                                                                                                               | Set Normal/Inverse Display        | X <sub>0</sub> =0: normal display (POR)<br>X <sub>0</sub> =1: inverse display                                                                                                                      |  |  |  |  |  |  |  |

| 1010111X <sub>0</sub>                                                                                                               | Set Display On/Off                | X <sub>0</sub> =0: turns off OLED panel (POR)<br>X <sub>0</sub> =1: turns on OLED panel                                                                                                            |  |  |  |  |  |  |  |

| 1011X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                                                                     | Set Page Address                  | Set GDDRAM Page Address (0~8) for read/write using $X_3X_2X_1X_0$                                                                                                                                  |  |  |  |  |  |  |  |

| 1100X <sub>3</sub> * * *                                                                                                            | Set COM Output Scan Direction     | X <sub>3</sub> =0: normal mode (POR)<br>X <sub>3</sub> =1: remapped mode. COM0 to COM[N-1] becomes COM[N-1] to COM0 in Multiplex ratio is equal to N.                                              |  |  |  |  |  |  |  |

| 11100000                                                                                                                            | Set Read-Modify-Write Mode        | Read-Modify-Write mode will be entered in which the column address will not be increased during display data read. After POR, Read-modify-write mode is turned OFF                                 |  |  |  |  |  |  |  |

| 11100010                                                                                                                            | Software Reset                    | Initialize internal status registers                                                                                                                                                               |  |  |  |  |  |  |  |

| 11101110                                                                                                                            | Set End of Read-Modify-Write Mode | Exit Read-Modify-Write mode. RAM Column address before entering the mode will be restored. After POR, Read-modify-write mode is OFF.                                                               |  |  |  |  |  |  |  |

| 11100011                                                                                                                            | NOP                               | Command for No Operation                                                                                                                                                                           |  |  |  |  |  |  |  |

| 1111 * * * *                                                                                                                        | Set Test Mode                     | Reserved for IC testing. Do NOT use.                                                                                                                                                               |  |  |  |  |  |  |  |

| 10101110<br>10100101                                                                                                                | Set Sleep Mode                    | Sleep mode will be entered with two commands: Command 1: Turns off OLED panel Command 2: Set entire display on                                                                                     |  |  |  |  |  |  |  |

| Bit Pattern                                                                                                                         | Command                    | Description                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10101000                                                                                                                            | Set Multiplex Ratio        | To select multiplex ratio N from 2 to the maximum multiplex ratio (POR value) (including icon line).                                                                                                                                               |

| ** $X_5X_4X_3X_2X_1X_0$                                                                                                             |                            | Max. mux ratio: 65                                                                                                                                                                                                                                 |

|                                                                                                                                     |                            | $N= X_5 X_4 X_3 X_2 X_1 X_0 + 2$ , e.g. $N=0011111b+2=17$                                                                                                                                                                                          |

| 10101010<br>*10X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                                           | Set Frame Frequency        | Frame frequency is set by the following formula:                                                                                                                                                                                                   |

| 10101011<br>10X₅0X₃00X₀                                                                                                             | Set Bias Current Mode      | Set bias current level of segment output cell $X_5=0$ and $X_3=1$ and $X_0=0$ : Normal (POR) $X_5=1$ and $X_3=0$ and $X_0=1$ : Set low bias current level                                                                                          |

| 1101000X <sub>0</sub>                                                                                                               | Set Icon Mode              | $X_0=0$ : icon mode off (POR)<br>$X_0=1$ : icon mode on                                                                                                                                                                                            |

| 11010011<br>**X <sub>5</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                             | Set Display Offset         | X <sub>5</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> :000000=no scroll by row (POR)<br><br>111111=scroll by 63 rows                                                                                           |

| 11011000<br>00000X <sub>2</sub> 0X <sub>0</sub>                                                                                     | Set Low Power Display Mode | $X_2$ =0 and $X_0$ =0: Normal (POR)<br>$X_2$ =1 and $X_0$ =1: Set low power consumption                                                                                                                                                            |

| 11011001<br>X <sub>7</sub> X <sub>6</sub> X <sub>5</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | Set Precharge Period       | $\begin{split} X_7X_6X_5X_4: & \text{ Set precharge period (POR=1000)} \\ & [Invalid entry for $X_7X_6X_5X_4$=0001 or 0000] \\ X_3X_2X_1X_0=1000: & \text{Normal (POR)} \\ X_3X_2X_1X_0=0011: & \text{For low precharge period usage} \end{split}$ |

| 11011010<br>***1**X <sub>1</sub> 0                                                                                                  | Set Current Mode           | X <sub>1</sub> =0: Select half range current mode (POR) X <sub>1</sub> =1: Select full range current mode                                                                                                                                          |

Note: Remark "\*" stands for "Don' t Care"

#### Read command table (D/C#=0, R/W#(WR#)=1, E(RD#)=1 for 6800 or E(RD#)=0 for 8080)

| Bit Pattern                                                                                                             | Command              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> | Status Register Read | $D_7$ =0: indicates the driver is ready for command.<br>$D_7$ =1: indicates the driver is Busy.<br>$D_6$ =0: indicates reverse segment mapping with column address<br>$D_6$ =1: indicates normal segment mapping with column address<br>$D_5$ =0: indicates the display is ON<br>$D_5$ =1: indicates the display is OFF<br>$D_4$ =0: initialization is not in progress<br>$D_4$ =1: initialization is in progress after RES# or software reset |

Note: Patterns other than that given in Command Table are prohibited to enter to the chip as a command; otherwise, unexpected result will occur.

# **6. Optical Characteristics**

6.1 Optical Characteristics

V<sub>LCD</sub>=16.8V Ta=25

| of option characteristics |             |        |           |                   |      |      | 10.0 1 | 1 4 25 |      |

|---------------------------|-------------|--------|-----------|-------------------|------|------|--------|--------|------|

| Item                      |             | Symbol | Condition |                   |      | Min. | Тур.   | Max.   | Unit |

|                           |             |        |           | y=0 °             | MAIN | -    | -40+35 |        |      |

| Viouvina                  | Anala       | X      | C > 2     | y-0               | SUB  | _    | -6036  |        |      |

| Viewing                   | Angle       |        | Cr≥2      | <sub>x</sub> =0 ° | MAIN | -    | -30+30 | )      | Deg  |

|                           |             | у      |           | x-0               | SUB  | _    | -4240  |        |      |

| Contrast Ratio            |             | Cr     |           | x=0 ° $y=0$ °     |      | 30   | 50     | 60     | ı    |

| Response                  | Turn<br>on  | Ton    |           | <sub>x</sub> =0 ° |      | -    | -      | 150    | ma   |

| Time                      | Turn<br>off | Toff   |           | y=0 °             |      | _    | -      | 100    | ms   |

|                           | Red         | X      |           | x=0 °             |      | -    | 0.43   | -      | ı    |

| Color                     | Red         | y      | y=0 °     | y=0 °             |      | _    | 0.35   | -      | 1    |

| Of CIE<br>Coord-          | Green       | X      |           | <sub>x</sub> =0 ° |      | -    | 0.32   | -      | -    |

| Inate                     | Olcell      | у      |           | y=0 °             |      | _    | 0.46   | -      | -    |

|                           | Plue        | X      |           | <sub>x</sub> =0 ° |      | _    | 0.22   | -      | _    |

|                           | Blue        | у      |           | y=0 °             |      | _    | 0.26   | -      | _    |

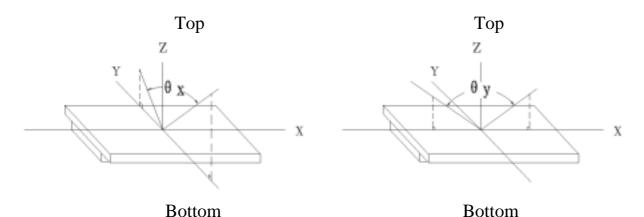

#### 6.2 Definition of Optical Characteristics

## 6.2.1 Definition of Viewing Angle

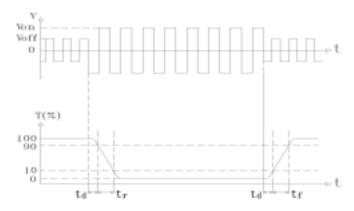

6.2.2 Definition of Contrast Ratio

# Curve of selected segment Curve of unselected segment

Contrast Ratio =  $B2/B1 = \frac{\text{unselected state brightness}}{\text{selected state brightness}}$

Measuring Conditions:

1) Ambient Temperature: 25 ; 2) Frame frequency: 70.0Hz 6.2.3 Definition of Response time

Turn on time:  $t_{o\,n}=t_{\rm d}+t_{\rm r}$  Turn off time:  $t_{o\,f\,f}=t_{\rm d}+t_{\rm f}$  Measuring Condition:

- 1) Operating Voltage:MAIN-LCD 16.8V SUB-LCD 9V

- 2) Frame frequency: 70.0Hz

## 6.3 Brightness Characteristic

| Item       | Symbol | Condition | Min. | Тур. | Max. | Unit              |

|------------|--------|-----------|------|------|------|-------------------|

| Brightness | Вр     | Ta=25 ±3  | 100  | -    | -    | cd/m <sup>2</sup> |

| Uniformity | Вр     | 30-80%RH  | -    | -    | 60   | %                 |

#### Note:

- 1. The data is measured after LEDs are turned on for 5 minutes.

- 2. Testing conditions LED: V<sub>LED</sub> = 270 V (AC) LCD: All dots are on (White color)

- 3. Brightness in the center of the LCD panel.

- 4. Definition of Uniformity ( Bp)

Bp = Bp (Min.) / Bp (Max.) X 100 (%)

Bp (Max.) = Maximum brightness in 9 measurement spots

Bp (Min.) = Minimum brightness in 9 measurement spots

# 7. Reliability

7.1 Content of Reliability Test

Ta=25

| No. | Test Item                          | Content of Test                                                                        | Test condition                                    |  |  |

|-----|------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------|--|--|

| 1   | High Temperature<br>Storage        | Endurance test applying the high storage temperature for a long time                   | 80 ±2 240H<br>Restore 4H at 25                    |  |  |

|     |                                    |                                                                                        |                                                   |  |  |

| 2   | Low Temperature Storage            | Endurance test applying the low storage temperature for a long time                    | -30 ±2 240H<br>Restore 4H at 25                   |  |  |

| 3   | High Temperature /Humidity Storage | Endurance test applying the high temperature and high humidity storage for a long time | 70 ±2 90%RH<br>240H<br>Restore 4H at 25           |  |  |

| 4   | Temperature<br>Cycle               | Endurance test applying the low and high temperature cycle  -30                        |                                                   |  |  |

|     |                                    | 1 cycle                                                                                | Restore 4H at 25                                  |  |  |

| 5   | Vibration Test<br>(package state)  | Endurance test applying the vibration during transportation                            | 10Hz~150Hz,<br>100m/s²,<br>120min                 |  |  |

| 6   | Shock Test (package state)         | Endurance test applying the shock during transportation                                | Half- sine wave,<br>300m/s <sup>2</sup> ,<br>18ms |  |  |

| 7   | Atmospheric<br>Pressure Test       | Endurance test applying the atmospheric pressure during transportation by air          | 25kPa 16H<br>Restore 2H                           |  |  |

7.2 Failure Judgment Criterion

| Criterion                   |                                                                        | Test Item No. |   |   |          |          |          |          |          | Failure Indeement Criterian         |

|-----------------------------|------------------------------------------------------------------------|---------------|---|---|----------|----------|----------|----------|----------|-------------------------------------|

| Item                        | 1                                                                      | 2             | 3 | 4 | 5        | 6        | 7        | 8        | 9        | Failure Judgement Criterion         |

| Basic<br>Specification      | <b>√</b>                                                               | <b>V</b>      | 1 | 1 | <b>V</b> | <b>V</b> | <b>√</b> | <b>√</b> | <b>√</b> | Out of the basic Specification      |

| Electrical specification    | <b>V</b>                                                               | <b>V</b>      | 1 | 1 | <b>V</b> |          |          |          |          | Out of the electrical specification |

| Mechanical<br>Specification |                                                                        |               |   |   |          |          | <b>V</b> | <b>V</b> |          | Out of the mechanical specification |

| Optical<br>Characteristic   | 1                                                                      | <b>V</b>      | 1 | 1 | <b>V</b> | <b>V</b> |          |          | <b>√</b> | Out of the optical specification    |

| Note                        | For test item refer to 8.1                                             |               |   |   |          |          |          |          |          |                                     |

| Remark                      | Basic specification = Optical specification + Mechanical specification |               |   |   |          |          |          |          |          |                                     |

8. Quality Level

| Examination                      | At T <sub>a</sub> =25                                                                        | Inspection     |          |       |    |                              |

|----------------------------------|----------------------------------------------------------------------------------------------|----------------|----------|-------|----|------------------------------|

| or Test                          | (unless otherwise stated)                                                                    | Min.           | Max.     | Unit  | IL | AQL                          |

| External<br>Visual<br>Inspection | Under normal illumination and eyesight condition, the distance between eyes and LCD is 25cm. | See Appendix A |          |       | II | Major<br>1.0<br>Minor<br>2.5 |

| Display<br>Defects               | Under normal illumination and eyesight condition, display on inspection.                     | See            | e Append | lix B | II | Major<br>1.0<br>Minor<br>2.5 |

Note: Major defects: Open segment or common, Short, Serious damages, Leakage

Miner defects: Others

Sampling standard conforms to GB2828

#### 9. Precautions for Use of LCD Modules

- 9.1 Handling Precautions

- 10.1.1 The display panel is made of glass. Do not subject it to a mechanical shock by dropping it from a high place, etc.

- 9.1.2 If the display panel is damaged and the liquid crystal substance inside it leaks out, be sure not to get any in your mouth, if the substance comes into contact with your skin or clothes, promptly wash it off using soap and water.

- 9.1.3 Do not apply excessive force to the display surface or the adjoining areas since this may cause the color tone to vary.

- 9.1.4 The polarizer covering the display surface of the LCD module is soft and easily scratched. Handle this polarizer carefully.

- 9.1.5 If the display surface is contaminated, breathe on the surface and gently wipe it with a soft dry cloth. If still not completely clear, moisten cloth with one of the following solvents:

- Isopropyl alcohol

- Ethyl alcohol

Solvents other than those mentioned above may damage the polarizer. Especially, do not use the following:

- Water

- Ketone

- Aromatic solvents

- 9.1.6 Do not attempt to disassemble the LCD Module.

- 9.1.7 If the logic circuit power is off, do not apply the input signals.

- 9.1.8 To prevent destruction of the elements by static electricity, be careful to maintain an optimum work environment.

- a. Be sure to ground the body when handling the LCD Modules.

- b. Tools required for assembly, such as soldering irons, must be properly ground.

- c. To reduce the amount of static electricity generated, do not conduct assembly and other work under dry conditions.

- d. The LCD Module is coated with a film to protect the display surface. Be care when peeling off this protective film since static electricity may be generated.

- 9.2 Storage precautions

- 9.2.1 When storing the LCD modules, avoid exposure to direct sunlight or to the light of fluorescent lamps.

- 9.2.2 The LCD modules should be stored under the storage temperature range.

If the LCD modules will be stored for a long time, the recommend condition is:

Temperature:  $0 \sim 40$

Relatively humidity: 80%

- 9.2.3 The LCD modules should be stored in the room without acid, alkali and harmful gas.

- 9.3 The LCD modules should be no falling and violent shocking during transportation, and also should avoid excessive press, water, damp and sunshine.

**Appendix A**Inspection items and criteria for appearance defects

| Items                  | Contents                   | Criteria                                |                            |                      |         |  |  |

|------------------------|----------------------------|-----------------------------------------|----------------------------|----------------------|---------|--|--|

| Leakage                |                            | Not permitted                           | Not permitted              |                      |         |  |  |

| Rainbow                |                            | According to                            | the lin                    | mit specimen         |         |  |  |

|                        | Wrong polarizer attachment | Not permitted                           | l                          |                      |         |  |  |

| Polarizer              | Bubble between             | Not counted                             |                            | Max. 3 defects al    | llowed  |  |  |

|                        | polarizer and glass        | φ<0.3mm                                 |                            | 0.3mm \$\phi\$ 0.51  | nm      |  |  |

|                        | Scratches of polarizer     | 8 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                            |                      |         |  |  |

| Black spot             |                            | Not counted                             | Max                        | Max. 3 spots allowed |         |  |  |

| (in viewing area)      | ا ا                        | X<0.2mm                                 | 0.2mm X 0.5mm Max.         |                      |         |  |  |

|                        |                            | X=(a+b)/2                               | spots<br>(lines)           |                      |         |  |  |

| Black line (in viewing |                            | Not counted                             | Max                        | . 3 lines allowed    | allowed |  |  |

| area)                  | o                          | a<0.02mm                                | 0.02mm a 0.05mm<br>b 2.0mm |                      |         |  |  |

| Progressive cracks     |                            | Not permitted                           | l                          |                      | ,       |  |  |

Appendix A

Inspection item and criteria for appearance defects (continued)

| Items  | Contents                   |                                    |                                                                                  |       | Criteria                                      |                             |                       |

|--------|----------------------------|------------------------------------|----------------------------------------------------------------------------------|-------|-----------------------------------------------|-----------------------------|-----------------------|

|        | Cracks on pads             | a                                  | b                                                                                | ١     | с                                             | Max. 2<br>cracks<br>allowed |                       |

|        |                            | 3mm                                | V                                                                                | V/5   | T/2                                           |                             |                       |

|        | b-4                        | 2mm                                | V                                                                                | V/5   | T/2 <c<t< td=""><td></td></c<t<>              |                             |                       |

|        | Cracks on contact side     | a                                  |                                                                                  |       | b                                             |                             |                       |

|        | /11/                       | 3m                                 | m                                                                                |       | T/2                                           |                             |                       |

|        |                            | 2m                                 | 2mm T/2 <b<t< td=""><td>Γ/2<b<t< td=""><td></td><td>M. 7</td></b<t<></td></b<t<> |       | Γ/2 <b<t< td=""><td></td><td>M. 7</td></b<t<> |                             | M. 7                  |

| Glass  |                            | C shall be not reach the seal area |                                                                                  |       |                                               | Max. 2 cracks               | Max. 5 cracks allowed |

| Cracks | Cracks on non-contact side | a                                  |                                                                                  | b     |                                               | allowed                     |                       |

|        | d - G                      | 3m                                 | m                                                                                | m T/2 |                                               |                             |                       |

|        |                            | 2m                                 | 2mm                                                                              |       | Γ/2 <b<t< td=""></b<t<>                       |                             |                       |

|        |                            | C 0.5mm                            |                                                                                  |       |                                               |                             |                       |

|        | 2"                         | d SW/                              | d SW/3                                                                           |       |                                               |                             |                       |

|        | Corner cracks              | e<2.0mn                            |                                                                                  |       |                                               | Max. 3                      |                       |

|        | f-P                        | f<2.0mn                            | 1 <sup>2</sup>                                                                   |       |                                               | cracks<br>allowed           |                       |

|        | e-1/                       |                                    |                                                                                  |       |                                               |                             |                       |

Appendix B

Inspection items and criteria for display defects

| Items                       |            | Contents    | Criteria           |                            |                    |  |  |

|-----------------------------|------------|-------------|--------------------|----------------------------|--------------------|--|--|

| Open segment or open common |            |             | Not permitted      |                            |                    |  |  |

| Short                       |            |             | Not permitted      | ı                          |                    |  |  |

| Wrong view                  | ing angle  |             | Not permitted      | ı                          |                    |  |  |

| Contrast radi               | o unevei   | 1           | According to       | the limit specimen         |                    |  |  |

| Crosstalk                   |            |             | According to       | the limit specimen         |                    |  |  |

|                             |            | 160         | Not counted        | Max.3 dots allowed         |                    |  |  |

|                             | Ť [        |             | X<0.1mm            | 0.1mm X 0.2mm              |                    |  |  |

| Pin holes                   | * <u> </u> |             | X=(a+b)/2          | Max.3 dots                 |                    |  |  |

| and cracks<br>in segment    |            | Not counted | Max.2 dots allowed | allowed                    |                    |  |  |

| (DOT)                       |            |             | A<0.1mm            | 0.1mm A 0.2mm<br>D<0.25mm  |                    |  |  |

| Black spot                  | not        |             | Not counted        | Max.3 spots allowed        |                    |  |  |

| (in viewing area)           |            |             | X<0.1mm            | 0.1mm X 0.2mm              |                    |  |  |

|                             | - a -      | X=(a+b)/2   | Spots              |                            |                    |  |  |

| Black line                  | D D        |             | Not counted        | Max.3 lines allowed        | (lines)<br>allowed |  |  |

| (in viewing area)           |            |             | a<0.02mm           | 0.02mm a 0.05mm<br>b 0.5mm |                    |  |  |

Appendix B

Inspection items and criteria for display defects (continued)

| Items                             | Content | Criteria                      |                        |               |

|-----------------------------------|---------|-------------------------------|------------------------|---------------|

|                                   | 10      | Not counted                   | Max. 2 defects allowed |               |

|                                   |         | x < 0.1mm                     | 0.1mm x 0.2mm          |               |

|                                   |         | x=(a+b)/2                     |                        |               |

|                                   | *       |                               |                        | Max.3 defects |

|                                   | D-711-a | Not counted                   | Max. 1 defects allowed | allowed       |

| Transfor-<br>mation<br>of segment |         | a < 0.1mm                     | 0.1mm a 0.2mm<br>D>0   |               |

|                                   |         | Max.2 defects<br>0.8W a 1.2   |                        |               |

|                                   | - W - a | a=measured va<br>W=nominal va |                        |               |